Modul 1.Percobaan.4. J-K flip flop dan D flip flop

19.41

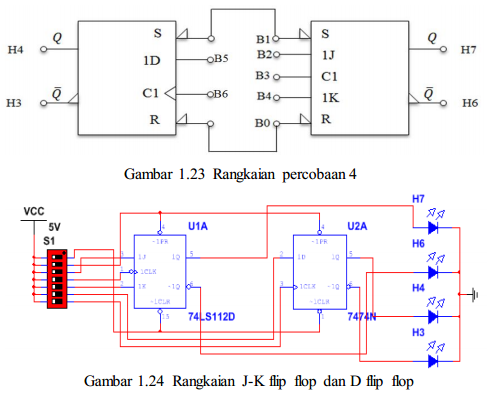

D. J-K flip flop dan D flip flop

Prosedur Percobaan:

1. Pastikan semua supply dalam keadaan off

2. Hubungkan jumper seperti rangkaian dibawah

3. periksakan rangkaian kepada asisten yang mengawas

4. Hidupkan semua supply

5. Tekan tombol Reset

6. Amati percobaan, jika tidak sesuai perbaiki rangkaian

7. Jika sesuai, maka selesai dan demokan pada asisten yang mengawas

8. Jelaskan prinsip kerja + teori dan hubungan keduanya kepada asisten

9. Demokan ke pembimbing praktikum

10 .Matikan supply

Prosedur Percobaan

1. Buatlah rangkaian seperti pada gambar berikut

2. Buatlah kondisi switch-switch seperti pada jurnal yang telah disediakan

3. Catat kondisi logika LED H0 & H1 nya.

2. Rangkaian Simulasi [kembali]

5. Jurnal [kembali]

6. Analisa [kembali]

1. Analisa Rangkaian Percobaan

Percobaan menggunakan blok dari JK Flip-Flop dan D Flip-Flop yang tampak pada hardware di atas. Nah masing masing dari Flip-Flop baik JK dan D, Set (S) dan R(Reset) dari masing masing Flip-Flop tersebut dihubungkan ke Saklar B1 dan B0.

Pada JK Flip-Flop input J nya dihubungkan ke saklar B2, input K ke saklar B4 dan input CKL ke saklar B3. Ouput Q dan ǭ Masing-masong dihubungkan ke LED H7 dan H6.

Pada D Flip-Flop, Input D nya dihubungkan ke saklar B5 dan input CLK ke saklar B6. Output Q dan ǭ masing-masing dihubungkan ke LED H4 dan H3. Tujuan Dihubungkannya Input ke Saklar adalah untuk memberikan nilai atau logika 0 atau pun 1. begitupun dengan output yang dihubungkan ke LED adalah untuk melihat logika yang dikeluarkan dari Flip-Flop.

Pada percobaan ini dilakukan mode-mode penggunaan dari JK Flip-Flop diantaranya :

- Mode Asinkronus Set: mode ini dibuat dengan cara memberikan input dari Reset bernilai 1 dan input dari Set bernilai 0, serta input J, K, dan CLK nya tidak dipedulikan.

- Mode Asinkronus Reset: mode ini dibuat dengan cara memberikan input Reset bernilai 0 dan input Set bernilai 1 serta input J, K, dan CLK tidak dipedulikan.

- Mode Terlarang: mode ini dibuat dengan memberikan Input Set dan Resetnya masing-masing bernilai 0 dan input J, K, dan CLK tidak dipedulikan.

- Mode Tetap: Mode ini dibuat dengan memberikan input Set dan Resetnya bernilai 1 dan input J dan K bernilai 0 serta input CLK diberikan pulsa (clock)

- Mode Reset: Mode ini dibuat dengan cara memberikan input Set dan reset bernilai 1 dan input J bernilai 0, K bernilai 1 serta input CLK diberi pulsa (clock)

- Mode Set: Mode ini dibuat dengan cara memberikan input 1 pada Set dan Reset dan input J bernilai 1, K bernilai 0 serta input CLK diberi clock.

- Mode Toggle: Mode ini dibuat dengan memberikan nilai input 1 pada set, reset, J dan K, dan input berupa clock pada CLK.

Pada percobaan juga dilakukan beberapa mode-mode dari penggunaan D Flip-Flop diantaranya:

- Asinkronus Set yang sama caraya dengan JK Flip-Flop di atas.

- Asinkronus Reset yang sama caranya dengan JK Flip-Flop di atas.

- Terlarang yang sama caranya dengan JK Flip-Flop di Atas.

- Set yang dibuat dengan memberikan logika 1 pada Set dan Reset serta 1 pada input D, dan Input Clocknya di cabut yang berarti memberikan transisi dari Low ke High.

- Reset yang dibuat dengan memberikan logika 1 pada Set dan Reset serta 0 pada input D, dan input clocknya dicabut yang berarti membrikan logika transisi dari low ke High.

2. Perbandingan Hasil Pada Praktikum dengan Tabel Kebenaran.

Dimulai dari JK Flip-Flop, Untuk membandingkannya berikut terdapat gambar tabel kebenaran dari JK Flip-Flop

(Sumber Gambar: http://ruanggemilang.blogspot.co.id/2014/10/flip-flop-j-k.html)

- Pertama yang akan dibandingkan adalah Nilai output saat digunakan pada mode asinkron set. Dimana pada jurnal Mode asinkron set terdapat pada nomor 2. Dapat dilihat Hasil dari output pada percobaan adalah untuk Q bernilai 1 dan ǭ bernilai 0 dimana sudah sesuai dengan Tabel kebenaran di atas.

- Kemudian perbandingan nilai ouput saat digunakan pada mode asinkron reset yaitu pada jurnal mode ini terdapat pada nomor 1. Dapat dilihat juga bahwa Nilai output Q adalah 0 dan ǭ adalah 1 yang juga sesuai dengan tabel kebenaran.

- Perbandingan nilai output pada saat digunakan pada mode terlarang dimana mode ini pada jurnal terdapat pada nomor 3 yang menghasilkan kedua outputnya adalah 0. nilai ini juga sesuai dengan tabel kebenaran.

- Perbandingan nilai output pada saat digunakan pada mode Hold atau tetap yang pada jurnal yaitu nomor 4. Ouput menghasilkan nilai yang sama dengan nilai sebelumnya yaitu 1. Ini juga sudah sesuai dengan tabel kebenaran di atas.

- Perbandingan dari nilai output pada saat digunakan pada mode reset yang pada jurnal yaitu nomor 5. Output pada mode ini menghasilkan Q bernilai 0 dan bernilai 1. Hasil ini juga menunjukkan persamaan dengan tabel kebenarannya.

- Perbandingan dari nilai output pada saat digunakan pada mode set yang pada jurnal yaitu nomor 6. Output pada mode ini menghasilkan Q bernilai 1 dan bernilai 0. Hasil juga menunjukkan kesamaan dengan tabel kebenaran di atas.

- Perbandingan dari nilai output pada saat digunakan pada mode toggle yang pada jurnal yaitu nomor 7. Output pada mode ini menghasilkan Q dan menghasilkan nilai yang berubah-ubah. Hasil juga menunjukkan kesamaan dengan tabel kebenaran di atas.

Untuk D Flip-Flop tabel kebenarannya dapat dilihat di bawah ini.

- Pertama yang akan dibandingkan adalah Nilai output saat digunakan pada mode asinkron set. Dimana pada jurnal Mode asinkron set terdapat pada nomor 2. Dapat dilihat Hasil dari output pada percobaan adalah untuk Q bernilai 1 dan ǭ bernilai 0 dimana sudah sesuai dengan Tabel kebenaran di atas.

- perbandingan nilai ouput saat digunakan pada mode asinkron reset yaitu pada jurnal mode ini terdapat pada nomor 1. Dapat dilihat juga bahwa Nilai output Q adalah 0 dan ǭ adalah 1 yang juga sesuai dengan tabel kebenaran.

- Perbandingan nilai output pada saat digunakan pada mode terlarang dimana mode ini pada jurnal terdapat pada nomor 3 yang menghasilkan kedua outputnya adalah 0. nilai ini juga sesuai dengan tabel kebenaran.

- Perbandingan nilai output saat digunakan pada mode Set yang terdapat pada nomor 5. Output yang terdapat pada Q adalah 1 dan ǭ adalah 0. Hasil ini sama dengan tabel kebenaran di atas.

- Perbandingan nilai output pada saat digunakan pada mode Reset yang terdapat pada nomor 4 di jurnal. Output pada Q dan bernilai 1. Hasil ini berbeda dengan Tabel kebenaran di atas yang seharusnya Q bernilai 0 dan ǭ bernilai 1.

7. Link Download [kembali]

File HTML - Download

File Rangkaian Simulasi - Download

File Video - Download